Мультиплексор и демультиплексор — различия между версиями

Gaporf (обсуждение | вклад) (→Логическая схема демультиплексора) |

м (rollbackEdits.php mass rollback) |

||

| (не показано 37 промежуточных версий 2 участников) | |||

| Строка 1: | Строка 1: | ||

| − | |||

| − | |||

| − | |||

{{Определение | {{Определение | ||

|definition='''Мультиплексор''' (англ. ''multiplexer'', или ''mux'') — [[Реализация булевой функции схемой из функциональных элементов|логическая схема]], имеющая <tex>2^n + n</tex> входов <tex>x_0</tex>, <tex>x_1</tex>, <tex>\ldots</tex>, <tex>x_{2^n-1}</tex>, <tex>s_0</tex>, <tex>s_1</tex>, <tex>\ldots</tex>, <tex>s_{n-1}</tex> и один выход <tex>z</tex>, на который подаётся значение на входе <tex>x_i</tex>, где <tex>i</tex> — число, которое кодируется входами <tex>s_0</tex>, <tex>s_1</tex>, <tex>\ldots</tex>, <tex>s_{n-1}</tex>. | |definition='''Мультиплексор''' (англ. ''multiplexer'', или ''mux'') — [[Реализация булевой функции схемой из функциональных элементов|логическая схема]], имеющая <tex>2^n + n</tex> входов <tex>x_0</tex>, <tex>x_1</tex>, <tex>\ldots</tex>, <tex>x_{2^n-1}</tex>, <tex>s_0</tex>, <tex>s_1</tex>, <tex>\ldots</tex>, <tex>s_{n-1}</tex> и один выход <tex>z</tex>, на который подаётся значение на входе <tex>x_i</tex>, где <tex>i</tex> — число, которое кодируется входами <tex>s_0</tex>, <tex>s_1</tex>, <tex>\ldots</tex>, <tex>s_{n-1}</tex>. | ||

| Строка 7: | Строка 4: | ||

{{Определение | {{Определение | ||

| − | |definition='''Демультиплексор''' (англ. ''demultiplexer'', или ''demux'') — логическая схема, имеющая <tex>n+1</tex> входов <tex>s_0</tex>, <tex>s_1</tex>, <tex>\ldots</tex>, <tex>s_{n-1}</tex>, <tex> | + | |definition='''Демультиплексор''' (англ. ''demultiplexer'', или ''demux'') — логическая схема, имеющая <tex>n+1</tex> входов <tex>s_0</tex>, <tex>s_1</tex>, <tex>\ldots</tex>, <tex>s_{n-1}</tex>, <tex>y</tex> и <tex>2^n</tex> выходов <tex>z_0</tex>, <tex>z_1</tex>, <tex>\ldots</tex>, <tex>z_{2^n-1}</tex>. На все выходы подаётся <tex>0</tex> кроме выхода <tex>z_i</tex>, на который подаётся значение на входе <tex>y</tex>, где <tex>i</tex> — число, которое кодируется входами <tex>s_0</tex>, <tex>s_1</tex>, <tex>\ldots</tex>, <tex>s_{n-1}</tex>. |

}} | }} | ||

| Строка 18: | Строка 15: | ||

===Мультиплексор 2-to-1=== | ===Мультиплексор 2-to-1=== | ||

| − | Рассмотрим мультиплексор <tex>2</tex>-to-<tex>1</tex> (это значит, что есть всего два входа <tex>x_0</tex> и <tex>x_1</tex>, значения которых могут подаваться на вход <tex>z</tex>). Переберём всевозможные варианты значений на входах. Если на <tex>s</tex> подавать <tex>0</tex>, то на выход <tex>z</tex> будет подаваться то же значение, которое подаётся на вход <tex>x_0</tex>, т.е. в данном случае значение на входе <tex>x_1</tex> нас не интересует. Аналогично, если на вход <tex>s</tex> подавать <tex>1</tex>, то на выход <tex>z</tex> будет подаваться то же значение, которое подаётся на вход <tex>x_1</tex> | + | Рассмотрим мультиплексор <tex>2</tex>-to-<tex>1</tex> (это значит, что есть всего два входа <tex>x_0</tex> и <tex>x_1</tex>, значения которых могут подаваться на вход <tex>z</tex>). Переберём всевозможные варианты значений на входах. Если на <tex>s</tex> подавать <tex>0</tex>, то на выход <tex>z</tex> будет подаваться то же значение, которое подаётся на вход <tex>x_0</tex>, т.е. в данном случае значение на входе <tex>x_1</tex> нас не интересует. Аналогично, если на вход <tex>s</tex> подавать <tex>1</tex>, то на выход <tex>z</tex> будет подаваться то же значение, которое подаётся на вход <tex>x_1</tex>. |

{| class="wikitable" | {| class="wikitable" | ||

| Строка 34: | Строка 31: | ||

===Мультиплексор 4-to-1=== | ===Мультиплексор 4-to-1=== | ||

| − | + | Рассмотрим мультиплексор <tex>4</tex>-to-<tex>1</tex> (это значит, что есть четыре входа <tex>x_0</tex>, <tex>x_1</tex>, <tex>x_2</tex> и <tex>x_3</tex>, значения которых могут подаваться на выход <tex>z</tex>). Также переберём всевозможные варианты значений на входах. Тут уже <tex>2</tex> входа <tex>s_0</tex> и <tex>s_1</tex>, которые определяют, значение какого из входов <tex>x_0</tex>, <tex>x_1</tex>, <tex>x_2</tex> или <tex>x_3</tex> будет подаваться на выход <tex>z</tex>. Если <tex>s_0 = s_1 = 0</tex>, то на выход <tex>z</tex> будет подаваться значение входа <tex>x_0</tex>, если <tex>s_0 = 1</tex> и <tex>s_1 = 0</tex> — то значение <tex>x_1</tex>, если <tex>s_0 = 0</tex> и <tex>s_1 = 1</tex> — то значение <tex>x_2</tex>, в противном случае — значение <tex>x_3</tex>. | |

| + | |||

{| class="wikitable" align="center" | {| class="wikitable" align="center" | ||

|- align="center" | |- align="center" | ||

| Строка 58: | Строка 56: | ||

==Логическая схема мультиплексора== | ==Логическая схема мультиплексора== | ||

| − | Заметим, что | + | {{main|Шифратор и дешифратор}} |

| + | |||

| + | Заметим, что дешифратор имеет <tex>n</tex> входов и <tex>2^n</tex> выходов, причём на все выходы дешифратора подаётся <tex>0</tex> кроме выхода <tex>z_i</tex>, на который подаётся <tex>1</tex>, где <tex>i</tex> — число, которое кодируется его входами. | ||

| − | Тогда давайте построим дешифратор <tex>n</tex>-to-<tex>2^n</tex> (это значит, что у дешифратора имеется <tex>n</tex> входов и <tex>2^n</tex> выходов), на вход ему подадим | + | Тогда давайте построим дешифратор <tex>n</tex>-to-<tex>2^n</tex> (это значит, что у дешифратора имеется <tex>n</tex> входов и <tex>2^n</tex> выходов), на вход ему подадим значения входов <tex>s_0</tex>, <tex>s_1</tex>, <tex>\ldots</tex>, <tex>s_{n-1}</tex>, а выходы этого дешифратора обозначим как <tex>y_0</tex>, <tex>y_1</tex>, <tex>\ldots</tex>, <tex>y_{2^n-1}</tex>, а потом с помощью гейта <tex>AND</tex> соединим выход <tex>y_i</tex> дешифратора с входом <tex>x_i</tex> мультиплексора, потом соединим все гейты с выходом <tex>z</tex> с помощью гейта <tex>OR</tex>, у которого <tex>2^n</tex> входов и один выход. Давайте разберёмся, почему эта схема правильная: очевидно, что если входы <tex>s_0</tex>, <tex>s_1</tex>, <tex>\ldots</tex> <tex>s_{n-1}</tex> кодируют вход <tex>i</tex>, то это значит, что только <tex>y_i</tex> выход дешифратора будет иметь <tex>1</tex>, тогда как на остальных выходах будет <tex>0</tex>, значит, что значения на входах <tex>x_0</tex>, <tex>x_1</tex>, <tex>\ldots</tex>, <tex>x_{i-1}</tex>, <tex>x_{i+1}</tex>, <tex>\ldots</tex>, <tex>x_{2^n-1}</tex> на ответ никак повлиять не могут. Теперь, если на входе <tex>x_i</tex> было <tex>0</tex>, то на выходе <tex>z</tex> будет <tex>0</tex>, если же на входе <tex>x_i</tex> был <tex>1</tex>, то на выходе <tex>z</tex> будет <tex>1</tex>. |

{| | {| | ||

| Строка 73: | Строка 73: | ||

===Демультиплексор 1-to-2=== | ===Демультиплексор 1-to-2=== | ||

| − | Рассмотрим демультиплексор <tex>1</tex>-to-<tex>2</tex> (это значит, что у демультиплексора два выхода). Если на вход <tex>s</tex> подать значение <tex>0</tex>, то на выход <tex>z_0</tex> будет подаваться то же значение, которое подаётся на вход <tex>y</tex>, а на выход <tex>z_1</tex> будет подаваться <tex>0</tex>. Если же на вход <tex>s</tex> подать значение <tex>1</tex>, то на выход <tex>z_0</tex> будет подаваться значение <tex>0</tex>, а на выход <tex>z_1</tex> то же значение, которое будет подаваться на вход <tex>y</tex> | + | Рассмотрим демультиплексор <tex>1</tex>-to-<tex>2</tex> (это значит, что у демультиплексора два выхода). Если на вход <tex>s</tex> подать значение <tex>0</tex>, то на выход <tex>z_0</tex> будет подаваться то же значение, которое подаётся на вход <tex>y</tex>, а на выход <tex>z_1</tex> будет подаваться <tex>0</tex>. Если же на вход <tex>s</tex> подать значение <tex>1</tex>, то на выход <tex>z_0</tex> будет подаваться значение <tex>0</tex>, а на выход <tex>z_1</tex> то же значение, которое будет подаваться на вход <tex>y</tex>. |

{| class="wikitable" | {| class="wikitable" | ||

| Строка 89: | Строка 89: | ||

===Демультиплексор 1-to-4=== | ===Демультиплексор 1-to-4=== | ||

| − | + | Рассмотрим демультиплексор <tex>1</tex>-to-<tex>4</tex> (это значит, что у демультиплексора четыре выхода). Теперь у нас уже есть два входа <tex>s_0</tex> и <tex>s_1</tex>, которые определяют, на какой из выходов <tex>z_0</tex>, <tex>z_1</tex>, <tex>z_2</tex> или <tex>z_3</tex> будет подаваться значение <tex>y</tex>, тогда как на остальные выходы будет подаваться <tex>0</tex>. В случае, когда <tex>s_0 = s_1 = 0</tex>, то на выход <tex>z_0</tex> будет подаваться значение на входе <tex>y</tex>, тогда как на <tex>z_1</tex>, <tex>z_2</tex> и <tex>z_3</tex> будет подаваться <tex>0</tex>. Если же <tex>s_0 = 1</tex> и <tex>s_1 = 0</tex>, то на выходы <tex>z_0</tex>, <tex>z_2</tex> и <tex>z_3</tex> будет подаваться <tex>0</tex>, а на выход <tex>z_1</tex> будет подаваться то же, что подаётся на вход <tex>y</tex>. Аналогично разбираются случаи <tex>s_0 = 0</tex>, <tex>s_1 = 1</tex> и <tex>s_0 = s_1 = 1</tex>. | |

{| class="wikitable" | {| class="wikitable" | ||

| Строка 121: | Строка 121: | ||

|[[Файл:LogicSircuit1to8demux.png|thumb|500px|Логическая схема демультиплексора <tex>1</tex>-to-<tex>8</tex>]] | |[[Файл:LogicSircuit1to8demux.png|thumb|500px|Логическая схема демультиплексора <tex>1</tex>-to-<tex>8</tex>]] | ||

|} | |} | ||

| + | |||

| + | ==Применение мультиплексора и демультиплексора в реальной жизни== | ||

| + | |||

| + | Мультиплексоры и демультиплексоры часто используются в электронных схемах. | ||

| + | |||

| + | В качестве примера можно рассмотреть использование мультиплексоров для разделения на временные слоты и предоставления каждому объекту логической цепи своего слота, во время которого можно обмениваться данными с другими объектами. Данный способ позволяет использовать как можно меньше проводов для соединения объектов между собою. Такой принцип применяется при построении телефонных станций, которые соединяются с помощью одного провода, а для обеспечения помехоустойчивой связи используются временные слоты, в которые только одна из станций может обмениваться данными с остальными. | ||

| + | |||

| + | Также мультиплексоры и демультиплексоры используются в современных телефонах для преобразование сигналов в голосовые сообщения, поскольку позволяют с помощью малого (порядка <tex>30</tex> входов) воспроизводить любой сигнал с частотой, которую может различить человеческое ухо. | ||

| + | |||

| + | Кроме того, мультиплексоры используются и при производстве компьютерных компонентов. | ||

==См. также== | ==См. также== | ||

*[[Реализация булевой функции схемой из функциональных элементов]] | *[[Реализация булевой функции схемой из функциональных элементов]] | ||

*[[Метод Лупанова синтеза схем]] | *[[Метод Лупанова синтеза схем]] | ||

| − | *[[ | + | *[[Шифратор и дешифратор]] |

==Источники информации== | ==Источники информации== | ||

*[https://en.wikipedia.org/wiki/Multiplexer Wikipedia - Multiplexer] | *[https://en.wikipedia.org/wiki/Multiplexer Wikipedia - Multiplexer] | ||

| + | *[https://books.google.ru/books?id=UD0h_GqgbHgC&printsec=frontcover&dq=network%2B+guide+to+networks&redir_esc=y#v=onepage&q&f=false Dean, Tamara (2010), Network+ Guide to Networks, стр. 79-84] | ||

[[Категория: Дискретная математика и алгоритмы]] | [[Категория: Дискретная математика и алгоритмы]] | ||

[[Категория: Схемы из функциональных элементов]] | [[Категория: Схемы из функциональных элементов]] | ||

Текущая версия на 19:11, 4 сентября 2022

| Определение: |

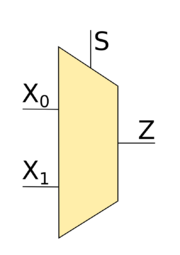

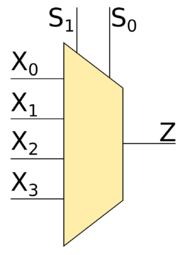

| Мультиплексор (англ. multiplexer, или mux) — логическая схема, имеющая входов , , , , , , , и один выход , на который подаётся значение на входе , где — число, которое кодируется входами , , , . |

| Определение: |

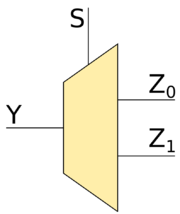

| Демультиплексор (англ. demultiplexer, или demux) — логическая схема, имеющая входов , , , , и выходов , , , . На все выходы подаётся кроме выхода , на который подаётся значение на входе , где — число, которое кодируется входами , , , . |

Содержание

Принцип работы мультиплексора

Мультиплексор 2-to-1

Рассмотрим мультиплексор -to- (это значит, что есть всего два входа и , значения которых могут подаваться на вход ). Переберём всевозможные варианты значений на входах. Если на подавать , то на выход будет подаваться то же значение, которое подаётся на вход , т.е. в данном случае значение на входе нас не интересует. Аналогично, если на вход подавать , то на выход будет подаваться то же значение, которое подаётся на вход .

Мультиплексор 4-to-1

Рассмотрим мультиплексор -to- (это значит, что есть четыре входа , , и , значения которых могут подаваться на выход ). Также переберём всевозможные варианты значений на входах. Тут уже входа и , которые определяют, значение какого из входов , , или будет подаваться на выход . Если , то на выход будет подаваться значение входа , если и — то значение , если и — то значение , в противном случае — значение .

Логическая схема мультиплексора

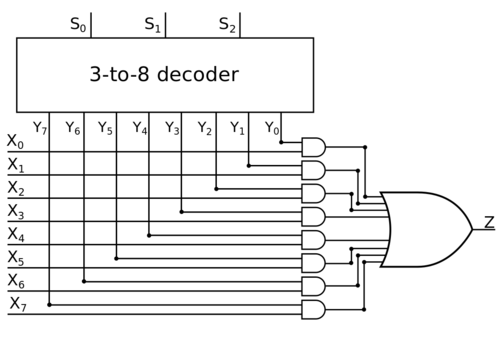

Заметим, что дешифратор имеет входов и выходов, причём на все выходы дешифратора подаётся кроме выхода , на который подаётся , где — число, которое кодируется его входами.

Тогда давайте построим дешифратор -to- (это значит, что у дешифратора имеется входов и выходов), на вход ему подадим значения входов , , , , а выходы этого дешифратора обозначим как , , , , а потом с помощью гейта соединим выход дешифратора с входом мультиплексора, потом соединим все гейты с выходом с помощью гейта , у которого входов и один выход. Давайте разберёмся, почему эта схема правильная: очевидно, что если входы , , кодируют вход , то это значит, что только выход дешифратора будет иметь , тогда как на остальных выходах будет , значит, что значения на входах , , , , , , на ответ никак повлиять не могут. Теперь, если на входе было , то на выходе будет , если же на входе был , то на выходе будет .

Принцип работы демультиплексора

Демультиплексор 1-to-2

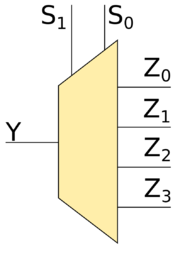

Рассмотрим демультиплексор -to- (это значит, что у демультиплексора два выхода). Если на вход подать значение , то на выход будет подаваться то же значение, которое подаётся на вход , а на выход будет подаваться . Если же на вход подать значение , то на выход будет подаваться значение , а на выход то же значение, которое будет подаваться на вход .

Демультиплексор 1-to-4

Рассмотрим демультиплексор -to- (это значит, что у демультиплексора четыре выхода). Теперь у нас уже есть два входа и , которые определяют, на какой из выходов , , или будет подаваться значение , тогда как на остальные выходы будет подаваться . В случае, когда , то на выход будет подаваться значение на входе , тогда как на , и будет подаваться . Если же и , то на выходы , и будет подаваться , а на выход будет подаваться то же, что подаётся на вход . Аналогично разбираются случаи , и .

Логическая схема демультиплексора

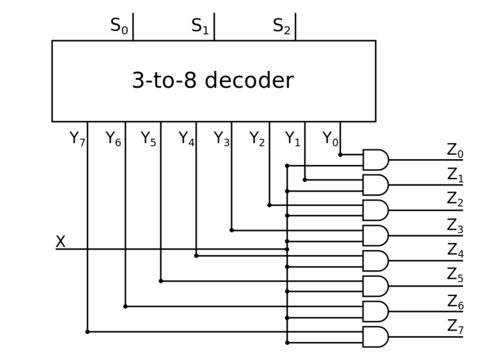

Построим схему, аналогичную схеме мультиплексора.

Тогда давайте построим дешифратор, -to-, на входы дешифратора подадим входы , , , , а выходы этого дешифратора мы обозначим как , , , . Поставим гейтов и соединим каждый из выходов дешифратора , , , со входом с помощью гейта , потом соединим соответственные гейты с выходами , , , , причем мы соединим гейт с выходом , если на этот гейт приходится выход дешифратора .

Применение мультиплексора и демультиплексора в реальной жизни

Мультиплексоры и демультиплексоры часто используются в электронных схемах.

В качестве примера можно рассмотреть использование мультиплексоров для разделения на временные слоты и предоставления каждому объекту логической цепи своего слота, во время которого можно обмениваться данными с другими объектами. Данный способ позволяет использовать как можно меньше проводов для соединения объектов между собою. Такой принцип применяется при построении телефонных станций, которые соединяются с помощью одного провода, а для обеспечения помехоустойчивой связи используются временные слоты, в которые только одна из станций может обмениваться данными с остальными.

Также мультиплексоры и демультиплексоры используются в современных телефонах для преобразование сигналов в голосовые сообщения, поскольку позволяют с помощью малого (порядка входов) воспроизводить любой сигнал с частотой, которую может различить человеческое ухо.

Кроме того, мультиплексоры используются и при производстве компьютерных компонентов.

См. также

- Реализация булевой функции схемой из функциональных элементов

- Метод Лупанова синтеза схем

- Шифратор и дешифратор