Мультиплексор и демультиплексор — различия между версиями

Gaporf (обсуждение | вклад) |

Gaporf (обсуждение | вклад) (→Модуль памяти) |

||

| Строка 127: | Строка 127: | ||

Допустим, что нам нужно реализовать модуль памяти на 8 бит. Обозначим эти биты как <tex>s_0</tex>, <tex>s_1</tex>, <tex>\ldots</tex>, <tex>s_7</tex>. Также допустим, что у нас есть следующие входы: <tex>a_0</tex>, <tex>a_1</tex>, <tex>a_2</tex>, которые задают номер бита, который следует обработать, также есть вход <tex>R/W</tex>, значение на котором равно <tex>0</tex>, если надо прочитать значение <tex>i</tex>-го бита, где <tex>i</tex> - число, которое кодируется входами <tex>A_0</tex>, <tex>A_1</tex>, <tex>A_2</tex> и вывести его на выход <tex>Q</tex>, или <tex>1</tex>, если надо записать в <tex>i</tex>-ый бит значение на входе <tex>D</tex>. Также есть вход <tex>C</tex> - провод синхронизации. | Допустим, что нам нужно реализовать модуль памяти на 8 бит. Обозначим эти биты как <tex>s_0</tex>, <tex>s_1</tex>, <tex>\ldots</tex>, <tex>s_7</tex>. Также допустим, что у нас есть следующие входы: <tex>a_0</tex>, <tex>a_1</tex>, <tex>a_2</tex>, которые задают номер бита, который следует обработать, также есть вход <tex>R/W</tex>, значение на котором равно <tex>0</tex>, если надо прочитать значение <tex>i</tex>-го бита, где <tex>i</tex> - число, которое кодируется входами <tex>A_0</tex>, <tex>A_1</tex>, <tex>A_2</tex> и вывести его на выход <tex>Q</tex>, или <tex>1</tex>, если надо записать в <tex>i</tex>-ый бит значение на входе <tex>D</tex>. Также есть вход <tex>C</tex> - провод синхронизации. | ||

| − | Давайте для хранения значения в <tex>i</tex>-ом бите будем использовать [[Триггеры#D-триггер|D-триггер]]. Если на входе <tex>c</tex> записано значение <tex>0</tex>, то нам не важно, что находится на выходе <tex>Q</tex>, поэтому эту ситуацию можно свести к ситуации, когда на <tex>C</tex> подано <tex>1</tex>, а на <tex>R/W</tex> - <tex>0</tex>. Теперь осталось реализовать операции чтения и записи. Подадим | + | Давайте для хранения значения в <tex>i</tex>-ом бите будем использовать [[Триггеры#D-триггер|D-триггер]]. Если на входе <tex>c</tex> записано значение <tex>0</tex>, то нам не важно, что находится на выходе <tex>Q</tex>, поэтому эту ситуацию можно свести к ситуации, когда на <tex>C</tex> подано <tex>1</tex>, а на <tex>R/W</tex> - <tex>0</tex>. Теперь осталось реализовать операции чтения и записи. Подадим на входы <tex>S_0</tex>, <tex>S_1</tex>, <tex>S_2</tex> демультиплексора значения на входах <tex>A_0</tex>, <tex>A_1</tex>, <tex>A_2</tex>, а на вход демультиплексора <tex>Y</tex> подадим на вход значение гейта <tex>AND</tex>, которому на вход подаются входы <tex>R/W</tex> и <tex>C</tex>. Тогда если либо на входе <tex>R/W</tex> <tex>0</tex>, либо на входе <tex>C</tex> подать <tex>0</tex> то на выходе демультиплексора будут все <tex>0</tex>. Если же и на <tex>R/W</tex> и на <tex>C</tex> подать <tex>1</tex>, то на выходе <tex>Z_i</tex> будет<tex>1</tex>, а на остальных - <tex>0</tex>, где <tex>i</tex> - число, которое кодируется входами <tex>A_0</tex>, <tex>A_1</tex>, <tex>A_2</tex>. Соединим выходы <tex>Z_0</tex>, <tex>Z_1</tex>, <tex>\ldots</tex>, <tex>Z_7</tex> демультиплексора к входам <tex>C</tex> D-триггеров, причём мы соединим выход <tex>Z_i</tex> с триггером, который хранит значение <tex>i</tex>-го бита. Подадим значение на входе <tex>D</tex> элементы памяти на оставшиеся свободными входы триггеров. Если же <tex>R/W = 0</tex> или <tex>C = 0</tex>, то все триггеры вернут значения, которые в них записаны. Если же <tex>R/W = 1</tex> и <tex>C = 1</tex>, то только в <tex>i</tex>-ый триггер запишется значение на входе <tex>D</tex>, тогда как на остальные триггеры на соответствующие им входы <tex>C</tex> будут подаваться <tex>0</tex>. Потом соединим <tex>i</tex>-ый триггер с <tex>X_i</tex> входом мультиплексора, также подадим значения на входах <tex>A_0</tex>, <tex>A_1</tex>, <tex>A_2</tex> на входы <tex>S_0</tex>, <tex>S_1</tex>, <tex>S_2</tex> мультиплексора. Тогда мультиплексор на выход <tex>Z</tex> выдаст значение, которое подаётся на <tex>X_i</tex>-ый вход, причём на <tex>Q</tex> всегда будет подаваться значение на <tex>i</tex>-ом бите независимо от значения на входе <tex>R/W</tex>, т.к. если был запрос "Записать в <tex>i</tex>-ый бит значение <tex>D</tex>, то неважно, что будет на выходе <tex>Q</tex>". |

{| | {| | ||

Версия 21:45, 10 декабря 2018

| Определение: |

| Мультиплексор (англ. multiplexer, или mux) — логическая схема, имеющая входов , , , , , , , и один выход , на который подаётся значение на входе , где — число, которое кодируется входами , , , . |

| Определение: |

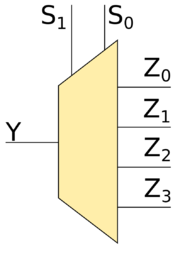

| Демультиплексор (англ. demultiplexer, или demux) — логическая схема, имеющая входов , , , , и выходов , , , . На все выходы подаётся кроме выхода , на который подаётся значение на входе , где — число, которое кодируется входами , , , . |

Содержание

Принцип работы мультиплексора

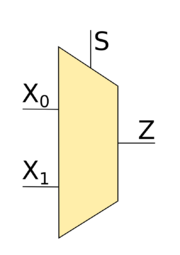

Мультиплексор 2-to-1

Рассмотрим мультиплексор -to- (это значит, что есть всего два входа и , значения которых могут подаваться на вход ). Переберём всевозможные варианты значений на входах. Если на подавать , то на выход будет подаваться то же значение, которое подаётся на вход , т.е. в данном случае значение на входе нас не интересует. Аналогично, если на вход подавать , то на выход будет подаваться то же значение, которое подаётся на вход . Для более лучшего понимания посмотрим на таблицу истинности.

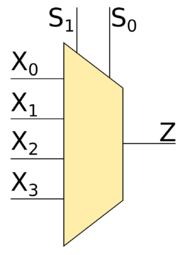

Мультиплексор 4-to-1

Также рассмотрим мультиплексор -to- (это значит, что есть четыре входа , , и , значения которых могут подаваться на выход ). Также переберём всевозможные варианты значений на входах. Тут уже входа и , которые определяют, значение какого из входов , , или будет подаваться на выход . Если , то на выход будет подаваться значение входа , если и — то значение , если и — то значение , в противном случае — значение . Для более лучшее понимания рекомендуется обратиться к таблице истинности.

Логическая схема мультиплексора

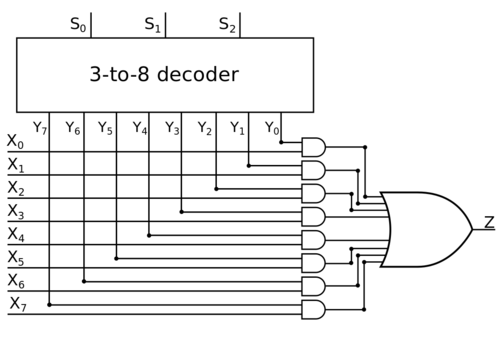

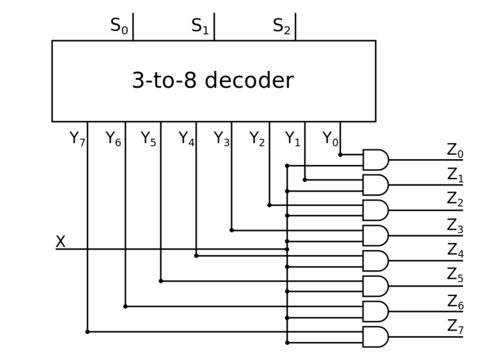

Заметим, что дешифратор имеет входов и выходов, причём на все выходы дешифратора подаётся кроме выхода , на который подаётся , где — число, которое кодируется его входами.

Тогда давайте построим дешифратор -to- (это значит, что у дешифратора имеется входов и выходов), на вход ему подадим входы , , , , а выходы этого дешифратора обозначим как , , , , а потом с помощью гейта соединим выход дешифратора с входом мультиплексора, потом соединим все гейты с выходом . Давайте разберёмся, почему эта схема правильная: очевидно, что если входы , , кодируют вход , то это значит, что только выход дешифратора будет иметь , тогда как на остальных выходах будет , значит, что значения на входах , , , , , , на ответ никак повлиять не могут. Теперь, если на входе было , то на выходе будет , если же на входе был , то на выходе будет .

Принцип работы демультиплексора

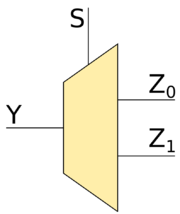

Демультиплексор 1-to-2

Рассмотрим демультиплексор -to- (это значит, что у демультиплексора два выхода). Если на вход подать значение , то на выход будет подаваться то же значение, которое подаётся на вход , а на выход будет подаваться . Если же на вход подать значение , то на выход будет подаваться значение , а на выход то же значение, которое будет подаваться на вход . Для более лучшего понимания посмотрим на таблицу истинности.

Демультиплексор 1-to-4

Также рассмотрим демультиплексор -to- (это значит, что у демультиплексора четыре выхода). Теперь у нас уже есть два входа и , которые определяют, на какой из выходов , , или будет подаваться значение , тогда как на остальные выходы будет подаваться . В случае, когда , то на выход будет подаваться значение на входе , тогда как на , и будет подаваться . Если же и , то на выходы , и будет подаваться , а на выход будет подаваться то же, что подаётся на вход . Аналогично разбираются случаи , и . Для более лучшего понимания посмотрим на таблицу истинности.

Логическая схема демультиплексора

Построим схему, аналогичную схеме мультиплексора.

Тогда давайте построим дешифратор, -to-, на входы дешифратора подадим входы , , , , а выходы этого дешифратора мы обозначим как , , , . Поставим гейтов и соединим каждый из выходов дешифратора , , , со входом с помощью гейта , потом соединим соответственные гейты с выходами , , , , причем мы соединим гейт с выходом , если на этот гейт приходится выход дешифратора .

Применение мультиплексора и демультиплексора в реальной жизни

Модуль памяти

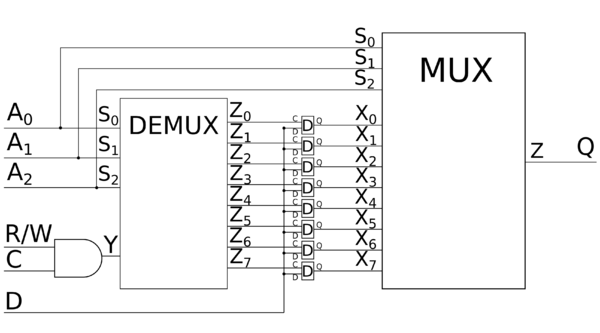

Допустим, что нам нужно реализовать модуль памяти на 8 бит. Обозначим эти биты как , , , . Также допустим, что у нас есть следующие входы: , , , которые задают номер бита, который следует обработать, также есть вход , значение на котором равно , если надо прочитать значение -го бита, где - число, которое кодируется входами , , и вывести его на выход , или , если надо записать в -ый бит значение на входе . Также есть вход - провод синхронизации.

Давайте для хранения значения в -ом бите будем использовать D-триггер. Если на входе записано значение , то нам не важно, что находится на выходе , поэтому эту ситуацию можно свести к ситуации, когда на подано , а на - . Теперь осталось реализовать операции чтения и записи. Подадим на входы , , демультиплексора значения на входах , , , а на вход демультиплексора подадим на вход значение гейта , которому на вход подаются входы и . Тогда если либо на входе , либо на входе подать то на выходе демультиплексора будут все . Если же и на и на подать , то на выходе будет, а на остальных - , где - число, которое кодируется входами , , . Соединим выходы , , , демультиплексора к входам D-триггеров, причём мы соединим выход с триггером, который хранит значение -го бита. Подадим значение на входе элементы памяти на оставшиеся свободными входы триггеров. Если же или , то все триггеры вернут значения, которые в них записаны. Если же и , то только в -ый триггер запишется значение на входе , тогда как на остальные триггеры на соответствующие им входы будут подаваться . Потом соединим -ый триггер с входом мультиплексора, также подадим значения на входах , , на входы , , мультиплексора. Тогда мультиплексор на выход выдаст значение, которое подаётся на -ый вход, причём на всегда будет подаваться значение на -ом бите независимо от значения на входе , т.к. если был запрос "Записать в -ый бит значение , то неважно, что будет на выходе ".

См. также

- Реализация булевой функции схемой из функциональных элементов

- Метод Лупанова синтеза схем

- Дешифратор