Сумматор — различия между версиями

(Новая страница: «'''Сумматор''' — логический операционный узел, выполняющий арифметическое сложение двоичн…») |

м (rollbackEdits.php mass rollback) |

||

| (не показано 12 промежуточных версий 3 участников) | |||

| Строка 1: | Строка 1: | ||

'''Сумматор''' — логический операционный узел, выполняющий арифметическое сложение двоичных, троичных или n-ичных кодов двух (бинарный), трёх (тринарный) или n чисел (n-нарный). При арифметическом сложении выполняются и другие дополнительные операции: учёт знаков чисел, выравнивание порядков слагаемых и тому подобное. | '''Сумматор''' — логический операционный узел, выполняющий арифметическое сложение двоичных, троичных или n-ичных кодов двух (бинарный), трёх (тринарный) или n чисел (n-нарный). При арифметическом сложении выполняются и другие дополнительные операции: учёт знаков чисел, выравнивание порядков слагаемых и тому подобное. | ||

| − | + | ==Неполный сумматор== | |

| − | '''Неполный сумматор''' | + | '''Неполный сумматор''' — логическая схема имеющая два входа и два выхода (двухразрядный сумматор, бинарный сумматор). Позволяет вычислять сумму <tex>A+B</tex>, где <tex>A</tex> и <tex>B</tex> — это разряды двоичного числа, при этом результатом будут два бита <tex>S,C</tex>, где <tex>S</tex> — это бит суммы по модулю, а <tex>C</tex> — бит переноса. <tex>S = A \oplus B</tex>, <tex>C = A and B</tex>, <tex>sum = 2 \times C + S</tex>.<br /> |

| − | + | [[Файл:Half_Adder.png|Неполный сумматор]]<br /> | |

| − | '''Полный сумматор''' — логическая цепь, которая производит сложение трех битов, часто обозначаемых < | + | ==Полный сумматор== |

| + | '''Полный сумматор''' — логическая цепь, которая производит сложение трех битов, часто обозначаемых <tex>A</tex>, <tex>B</tex>, и <tex>C_{in}</tex>, где <tex>C_{in}</tex> — бит переноса из предыдущего разряда. Это позволяет построить схему двоичного сумматора (трёхразрядный сумматор, тринарный сумматор) На выход подаются два бита <tex>S,C_{out}</tex>, где <tex>S</tex> — это бит суммы по модулю, а <tex>C_{out}</tex> — бит переноса. <tex>C_{out} = <A , B , C></tex>, <tex>S = A \oplus B \oplus C</tex>, <tex>sum = 2 \times C_{out} + S</tex>.<br /> | ||

| + | [[Файл:Full_Adder.png|Полный сумматор]]<br /> | ||

| + | ==См. также== | ||

| + | * [[Реализация булевой функции схемой из функциональных элементов]] | ||

| + | * [[Изменение размера оптимальной схемы при переходе к другому базису]] | ||

| + | * [[Каскадный сумматор]] | ||

| + | * [[Двоичный каскадный сумматор]] | ||

| + | * [[Матричный умножитель]] | ||

| + | * [[Дерево Уоллеса]] | ||

| + | == Литература == | ||

| + | * Угрюмов Е. П. Элементы и узлы ЭЦВМ. М.: Высшая школа, 1976. — 232 с. | ||

| + | * Угрюмов Е. П. Цифровая схемотехника. — СПб.: БХВ-Петербург, 2001. — 528 с. | ||

| + | * Жан М. Рабаи, Ананта Чандракасан, Боривож Николич. 11. Проектирование арифметических блоков: Сумматор // Цифровые интегральные схемы. Методология проектирования = Digital Integrated Circuits. — 2-е изд. — М.: Вильямс, 2007. — С. 912. — ISBN 0-13-090996-3 | ||

Текущая версия на 19:10, 4 сентября 2022

Сумматор — логический операционный узел, выполняющий арифметическое сложение двоичных, троичных или n-ичных кодов двух (бинарный), трёх (тринарный) или n чисел (n-нарный). При арифметическом сложении выполняются и другие дополнительные операции: учёт знаков чисел, выравнивание порядков слагаемых и тому подобное.

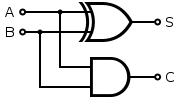

Неполный сумматор

Неполный сумматор — логическая схема имеющая два входа и два выхода (двухразрядный сумматор, бинарный сумматор). Позволяет вычислять сумму , где и — это разряды двоичного числа, при этом результатом будут два бита , где — это бит суммы по модулю, а — бит переноса. , , .

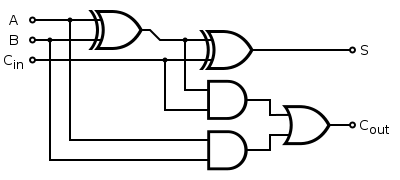

Полный сумматор

Полный сумматор — логическая цепь, которая производит сложение трех битов, часто обозначаемых , , и , где — бит переноса из предыдущего разряда. Это позволяет построить схему двоичного сумматора (трёхразрядный сумматор, тринарный сумматор) На выход подаются два бита , где — это бит суммы по модулю, а — бит переноса. , , .

См. также

- Реализация булевой функции схемой из функциональных элементов

- Изменение размера оптимальной схемы при переходе к другому базису

- Каскадный сумматор

- Двоичный каскадный сумматор

- Матричный умножитель

- Дерево Уоллеса

Литература

- Угрюмов Е. П. Элементы и узлы ЭЦВМ. М.: Высшая школа, 1976. — 232 с.

- Угрюмов Е. П. Цифровая схемотехника. — СПб.: БХВ-Петербург, 2001. — 528 с.

- Жан М. Рабаи, Ананта Чандракасан, Боривож Николич. 11. Проектирование арифметических блоков: Сумматор // Цифровые интегральные схемы. Методология проектирования = Digital Integrated Circuits. — 2-е изд. — М.: Вильямс, 2007. — С. 912. — ISBN 0-13-090996-3