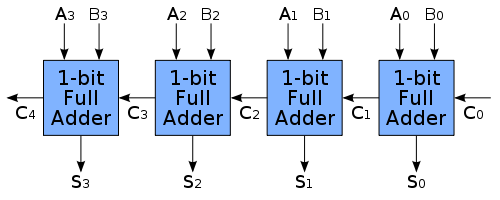

Каскадный сумматор

| Определение: |

| Каскадный сумматор — логическая схема, осуществляющая сложение многоразрядных двоичных чисел. |

Как известно, с помощью полного сумматора можно сложить 2 одноразрядных двоичных числа. Для сложения двух -разрядных двоичных чисел можно использовать полных сумматоров.

При сложении двух чисел в -том разряде складываются , и входной бит переноса (carry-in bit) . Младший разряд суммы записывается в -й разряд ответа (), а старший становится выходным битом переноса (carry-out bit) и используется при сложении в следующем разряде.

При этом в первый входной бит переноса подаётся ноль, а последний бит переноса даёт старший разряд суммы.

Прежде чем сложить -ые биты, надо ждать выходного бита переноса от сложения битов, то есть сумма в каждом разряде может зависеть от суммы предыдущих разрядов. Поэтому сложение с помощью каскадного сумматора выполняется за время .