Каскадный сумматор

| Определение: |

| Каскадный сумматор — логическая цепь, осуществляющая сложение многоразрядных двоичных чисел. |

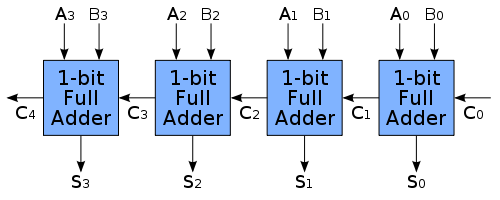

Как известно, с помощью полного сумматора можно сложить 2 одноразрядных двоичных числа. Для сложения двух N-разрядных двоичных чисел можно использовать N полных сумматоров. При сложении двух чисел в i-том разряде складываются , и входной бит переноса (carry-in bit) . Младший разряд суммы записывается в i-й разряд ответа (), а старший становится выходным битом переноса (carry-out bit) и используется при сложении в следующем разряде.

Составить схему на основе каскадного сумматора достаточно просто, но такой сумматор работает относительно медленно. Действительно, прежде чем сложить i-ые биты, надо ждать входного бита переноса от сложения битов. Таким образом, сложение происходит за время О(N).