Cумматор — различия между версиями

(→Полный сумматор) |

(→Литература) |

||

| Строка 16: | Строка 16: | ||

* [[Матричный умножитель]] | * [[Матричный умножитель]] | ||

* [[Дерево Уоллеса]] | * [[Дерево Уоллеса]] | ||

| − | == | + | == Источники информации == |

* Угрюмов Е. П. Элементы и узлы ЭЦВМ. М.: Высшая школа, 1976. — 232 с. | * Угрюмов Е. П. Элементы и узлы ЭЦВМ. М.: Высшая школа, 1976. — 232 с. | ||

* Угрюмов Е. П. Цифровая схемотехника. — СПб.: БХВ-Петербург, 2001. — 528 с. | * Угрюмов Е. П. Цифровая схемотехника. — СПб.: БХВ-Петербург, 2001. — 528 с. | ||

Версия 19:13, 19 ноября 2014

Сумматор (англ. adder) — логический операционный узел, выполняющий арифметическое сложение двоичных, троичных или -ичных кодов. Может складывать два (бинарный), три (тернарный) или чисел (-арный). Помимо сложения выполняются и другие операции: учёт знаков чисел, выравнивание порядков слагаемых и тому подобное.

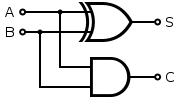

Неполный сумматор

Неполный сумматор (англ. half adder) — логическая схема, имеющая два входа и два выхода (двухразрядный сумматор, бинарный сумматор). Позволяет вычислять сумму , где и — это разряды двоичного числа. При этом результатом будут два бита и , где — это бит суммы по модулю , а — бит переноса. , , .

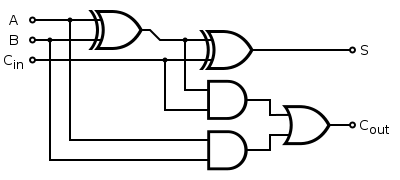

Полный сумматор

Полный сумматор (англ. full adder) — логическая схема, которая производит сложение трех битов, часто обозначаемых , и . На выход подаются два бита и , где — это бит суммы по модулю, а — бит переноса. , , .

Полный сумматор используется при построении двоичного каскадного сумматора.

См. также

- Реализация булевой функции схемой из функциональных элементов

- Изменение размера оптимальной схемы при переходе к другому базису

- Каскадный сумматор

- Двоичный каскадный сумматор

- Матричный умножитель

- Дерево Уоллеса

Источники информации

- Угрюмов Е. П. Элементы и узлы ЭЦВМ. М.: Высшая школа, 1976. — 232 с.

- Угрюмов Е. П. Цифровая схемотехника. — СПб.: БХВ-Петербург, 2001. — 528 с.

- Жан М. Рабаи, Ананта Чандракасан, Боривож Николич. 11. Проектирование арифметических блоков: Сумматор // Цифровые интегральные схемы. Методология проектирования = Digital Integrated Circuits. — 2-е изд. — М.: Вильямс, 2007. — С. 912. — ISBN 0-13-090996-3